| Карта сайта | |

| Недавние изменения | |

| Поиск | |

| Вы посетили | |

| История страницы | |

| Вход |

Содержание

Микропроцессор

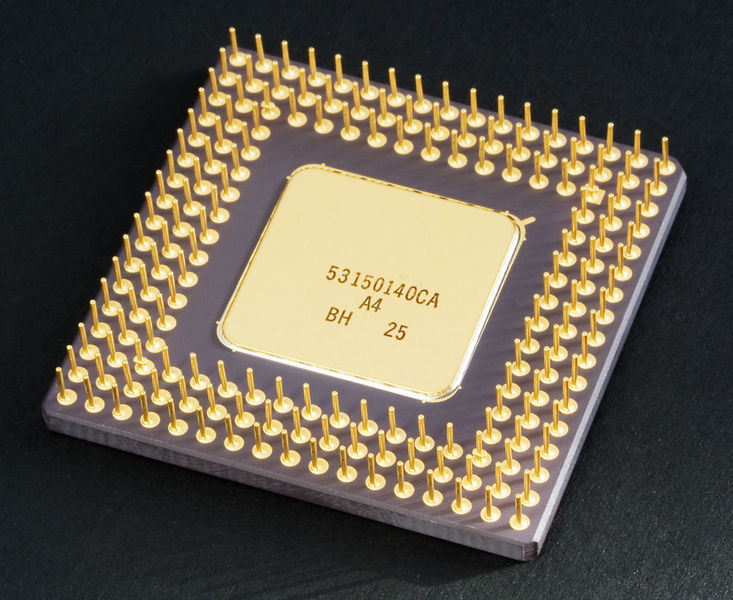

Микропроцессор (см.рисунок) обычно представляет собой отдельную микросхему или же часть микросхемы (в случае микроконтроллера). В прежние годы процессор иногда выполнялся на комплектах из нескольких микросхем, но сейчас от такого подхода уже практически отказались. Микросхема процессора обязательно имеет выводы трех шин: шины адреса, шины данных и шины управления. Иногда некоторые сигналы и шины мультиплексируются, чтобы уменьшить количество выводов микросхемы процессора.

Важнейшие характеристики процессора — это количество разрядов его шины данных, количество разрядов его шины адреса и количество управляющих сигналов в шине управления. Разрядность шины данных определяет скорость работы системы. Разрядность шины адреса определяет допустимую сложность системы. Количество линий управления определяет разнообразие режимов обмена и эффективность обмена процессора с другими устройствами системы.

Кроме выводов для сигналов трех основных шин процессор всегда имеет вывод (или два вывода) для подключения внешнего тактового сигнала или кварцевого резонатора (CLK), так как процессор всегда представляет собой тактируемое устройство. Чем больше тактовая частота процессора, тем он быстрее работает, то есть тем быстрее выполняет команды. Впрочем, быстродействие процессора определяется не только тактовой частотой, но и особенностями его структуры. Современные процессоры выполняют большинство команд за один такт и имеют средства для параллельного выполнения нескольких команд. Тактовая частота процессора не связана прямо и жестко со скоростью обмена по магистрали, так как скорость обмена по магистрали ограничена задержками распространения сигналов и искажениями сигналов на магистрали. То есть тактовая частота процессора определяет только его внутреннее быстродействие, а не внешнее. Иногда тактовая частота процессора имеет нижний и верхний пределы. При превышении верхнего предела частоты возможно перегревание процессора, а также сбои, причем, что самое неприятное, возникающие не всегда и нерегулярно. Так что с изменением этой частоты надо быть очень осторожным

Функции микропроцессора

После включения питания процессор переходит в первый адрес программы начального пуска и выполняет эту программу. Данная программа предварительно записана в постоянную (энергонезависимую) память. После завершения программы начального пуска процессор начинает выполнять основную программу, находящуюся в постоянной или оперативной памяти, для чего выбирает по очереди все команды. От этой программы процессор могут отвлекать внешние прерывания или запросы на ПДП. Команды из памяти процессор выбирает с помощью циклов чтения по магистрали. При необходимости процессор записывает данные в память или в устройства ввода/вывода с помощью циклов записи или же читает данные из памяти или из устройств ввода/вывода с помощью циклов чтения.

Таким образом, основные функции любого процессора следующие:

выборка (чтение) выполняемых команд; ввод (чтение) данных из памяти или устройства ввода/вывода; вывод (запись) данных в память или в устройства ввода/вывода; обработка данных (операндов), в том числе арифметические операции над ними; адресация памяти, то есть задание адреса памяти, с которым будет производиться обмен; обработка прерываний и режима прямого доступа. Упрощенно структуру микропроцессора можно представить в следующем виде

Основные функции показанных узлов следующие.

Схема управления выборкой команд выполняет чтение команд из памяти и их дешифрацию. В первых микропроцессорах было невозможно одновременное выполнение предыдущей команды и выборка следующей команды, так как процессор не мог совмещать эти операции. Но уже в 16-разрядных процессорах появляется так называемый конвейер (очередь) команд, позволяющий выбирать несколько следующих команд, пока выполняется предыдущая. Два процесса идут параллельно, что ускоряет работу процессора. Конвейер представляет собой небольшую внутреннюю память процессора, в которую при малейшей возможности (при освобождении внешней шины) записывается несколько команд, следующих за исполняемой. Читаются эти команды процессором в том же порядке, что и записываются в конвейер (это память типа FIFO, First In — First Out, первый вошел — первый вышел). Правда, если выполняемая команда предполагает переход не на следующую ячейку памяти, а на удаленную (с меньшим или большим адресом), конвейер не помогает, и его приходится сбрасыва ть. Но такие команды встречаются в программах сравнительно редко.

Развитием идеи конвейера стало использование внутренней кэш-памяти процессора, которая заполняется командами, пока процессор занят выполнением предыдущих команд. Чем больше объем кэш-памяти, тем меньше вероятность того, что ее содержимое придется сбросить при команде перехода. Понятно, что обрабатывать команды, находящиеся во внутренней памяти, процессор может гораздо быстрее, чем те, которые расположены во внешней памяти. В кэш-памяти могут храниться и данные, которые обрабатываются в данный момент, это также ускоряет работу. Для большего ускорения выборки команд в современных процессорах применяют совмещение выборки и дешифрации, одновременную дешифрацию нескольких команд, несколько параллельных конвейеров команд, предсказание команд переходов и некоторые другие методы.

Арифметико-логическое устройство (или АЛУ, ALU) предназначено для обработки информации в соответствии с полученной процессором командой. Примерами обработки могут служить логические операции (типа логического «И», «ИЛИ», «Исключающего ИЛИ» и т.д.) то есть побитные операции над операндами, а также арифметические операции (типа сложения, вычитания, умножения, деления и т.д.). Над какими кодами производится операция, куда помещается ее результат — определяется выполняемой командой. Если команда сводится всего лишь к пересылке данных без их обработки, то АЛУ не участвует в ее выполнении.

Быстродействие АЛУ во многом определяет производительность процессора. Причем важна не только частота тактового сигнала, которым тактируется АЛУ, но и количество тактов, необходимое для выполнения той или иной команды. Для повышения производительности разработчики стремятся довести время выполнения команды до одного такта, а также обеспечить работу АЛУ на возможно более высокой частоте. Один из путей решения этой задачи состоит в уменьшении количества выполняемых АЛУ команд, создание процессоров с уменьшенным набором команд (так называемые RISC-процессоры). Другой путь повышения производительности процессора — использование нескольких параллельно работающих АЛУ.

Что касается операций над числами с плавающей точкой и других специальных сложных операций, то в системах на базе первых процессоров их реализовали последовательностью более простых команд, специальными подпрограммами, однако затем были разработаны специальные вычислители — математические сопроцессоры, которые заменяли основной процессор на время выполнения таких команд. В современных микропроцессорах математические сопроцессоры входят в структуру как составная часть.

Регистры процессора представляют собой по сути ячейки очень быстрой памяти и служат для временного хранения различных кодов: данных, адресов, служебных кодов. Операции с этими кодами выполняются предельно быстро, поэтому, в общем случае, чем больше внутренних регистров, тем лучше. Кроме того, на быстродействие процессора сильно влияет разрядность регистров. Именно разрядность регистров и АЛУ называется внутренней разрядностью процессора, которая может не совпадать с внешней разрядностью.

По отношению к назначению внутренних регистров существует два основных подхода. Первого придерживается, например, компания Intel, которая каждому регистру отводит строго определенную функцию. С одной стороны, это упрощает организацию процессора и уменьшает время выполнения команды, но с другой — снижает гибкость, а иногда и замедляет работу программы. Например, некоторые арифметические операции и обмен с устройствами ввода/вывода проводятся только через один регистр — аккумулятор, в результате чего при выполнении некоторых процедур может потребоваться несколько дополнительных пересылок между регистрами. Второй подход состоит в том, чтобы все (или почти все) регистры сделать равноправными, как , например, в 16-разрядных процессорах Т-11 фирмы DEC. При этом достигается высокая гибкость, но необходимо усложнение структуры процессора. Существуют и промежуточные решения, в частности, в процессоре MC68000 фирмы Motorola половина регистров использовалась для данных, и они были взаимозаменяемы, а другая половина — для адресов, и они также взаимозаменяемы.

Регистр признаков (регистр состояния) занимает особое место, хотя он также является внутренним регистром процессора. Содержащаяся в нем информация — это не данные, не адрес, а слово состояния процессора (ССП, PSW — Processor Status Word). Каждый бит этого слова (флаг) содержит информацию о результате предыдущей команды. Например, есть бит нулевого результата, который устанавливается в том случае, когда результат выполнения предыдущей команды — нуль, и очищается в том случае, когда результат выполнения команды отличен от нуля. Эти биты (флаги) используются командами условных переходов, например, командой перехода в случае нулевого результата. В этом же регистре иногда содержатся флаги управления, определяющие режим выполнения некоторых команд.

Схема управления прерываниями обрабатывает поступающий на процессор запрос прерывания, определяет адрес начала программы обработки прерывания (адрес вектора прерывания), обеспечивает переход к этой программе после выполнения текущей команды и сохранения в памяти (в стеке) текущего состояния регистров процессора. По окончании программы обработки прерывания процессор возвращается к прерванной программе с восстановленными из памяти (из стека) значениями внутренних регистров. Подробнее о стеке будет рассказано в следующем разделе.

Схема управления прямым доступом к памяти служит для временного отключения процессора от внешних шин и приостановки работы процессора на время предоставления прямого доступа запросившему его устройству.

Логика управления организует взаимодействие всех узлов процессора, перенаправляет данные, синхронизирует работу процессора с внешними сигналами, а также реализует процедуры ввода и вывода информации.

Таким образом, в ходе работы процессора схема выборки команд выбирает последовательно команды из памяти, затем эти команды выполняются, причем в случае необходимости обработки данных подключается АЛУ. На входы АЛУ могут подаваться обрабатываемые данные из памяти или из внутренних регистров. Во внутренних регистрах хранятся также коды адресов обрабатываемых данных, расположенных в памяти. Результат обработки в АЛУ изменяет состояние регистра признаков и записывается во внутренний регистр или в память (как источник, так и приемник данных указывается в составе кода команды). При необходимости информация может переписываться из памяти (или из устройства ввода/вывода) во внутренний регистр или из внутреннего регистра в память (или в устройство ввода/вывода).

Внутренние регистры любого микропроцессора обязательно выполняют две служебные функции:

определяют адрес в памяти, где находится выполняемая в данный момент команда (функция счетчика команд или указателя команд); определяют текущий адрес стека (функция указателя стека). В разных процессорах для каждой из этих функций может отводиться один или два внутренних регистра. Эти два указателя отличаются от других не только своим специфическим, служебным, системным назначением, но и особым способом изменения содержимого. Их содержимое программы могут менять только в случае крайней необходимости, так как любая ошибка при этом грозит нарушением работы компьютера, зависанием и порчей содержимого памяти.

Содержимое указателя (счетчика) команд изменяется следующим образом. В начале работы системы (при включении питания) в него заносится раз и навсегда установленное значение. Это первый адрес программы начального запуска. Затем после выборки из памяти каждой следующей команды значение указателя команд автоматически увеличивается (инкрементируется) на единицу (или на два в зависимости от формата команд и типа процессора). То есть следующая команда будет выбираться из следующего по порядку адреса памяти. При выполнении команд перехода, нарушающих последовательный перебор адресов памяти, в указатель команд принудительно записывается новое значение — новый адрес в памяти, начиная с которого адреса команд опять же будут перебираться последовательно. Такая же смена содержимого указателя команд производится при вызове подпрограммы и возврате из нее или при начале обработки прерывания и после его окончания.

Характеристики

Здесь будут рассмотрены параметры наиболее важных устройств компьютера, таких как процессор и внутренняя память.

Начнем с процессора. Очевидно, что пользователя в первую очередь интересует его производительность, т.е. скорость выполнения предложенной процессору задачи. Традиционно быстродействие процессора измерялось путем определения количества операций в единицу времени, как правило, в секунду. До тех пор, пока машины выполняли только вычисления, такой показатель был достаточно удобен. Однако по мере развития вычислительной техники количество видов обрабатываемой информации возрастало, и обсуждаемый показатель перестал быть универсальным. В самом деле, в простейшем случае даже количество арифметических действий над целыми и над вещественными числами может для одного и того же компьютера отличаться на порядок! Что говорить о скорости обработки графической или видео информации, которые к тому же зависят не только от самого процессора, но и от устройства видеоблоков компьютера… Кроме того, современные процессоры, например, Pentium, имеют очень сложное внутренне устройство и могут выполнять машинные команды параллельно. Иными словами, процессор может одновременно выполнять несколько разных инструкций, а значит, время завершения команды уже зависит не только от нее самой, но и от «соседних» операций! Таким образом, количество выполняемых за секунду операций перестает быть постоянным и выбирать его в качестве характеристики процессора не очень удобно.

Именно поэтому сейчас получила широкое распространение другая характеристика скорости работы процессора – его тактовая частота. Рассмотрим данную величину подробнее. Любая операция процессора (машинная команда) состоит из отдельных элементарных действий – тактов. Для организации последовательного выполнения требуемых тактов друг за другом, в компьютере имеется специальный генератор импульсов, каждый из которых инициирует очередной такт машинной команды (какой именно, определяется устройством процессора и логикой выполняемой операции). Очевидно, что чем чаще следуют импульсы от генератора, тем быстрее будет выполнена операция, состоящая из фиксированного числа тактов. Из сказанного следует, что тактовая частота определяется количеством импульсов в секунду и измеряется в мегагерцах – т.е. миллионах импульсов за 1 сек. Разумеется, тактовая частота не может быть произвольно высокой, поскольку в какой-то момент процессор может просто «не успеть» выполнить очередной такт до прихода следующего импульса. Однако инженеры делают все возможное для повышения значения этой характеристики процессора, и на данный момент тактовая частота самых современных процессоров уже превышает 1000 МГц, т.е. 1 ГГц (1 гигагерц).

Следует четко представлять, что сравнение тактовых частот позволяет надежно определить, какой из двух процессоров более быстродействующий только в том случае, если оба процессора устроены примерно одинаково. Если же попытаться сравнить процессоры, произведенные разными изготовителями и работающие по разным принципам, можно получить абсолютно неправильные выводы. В самом деле, если в одном из процессоров команда выполняется за 2 такта, а в другом – за 3, то при совершенно одинаковой частоте первый будет работать в полтора раза быстрее! Кроме того, не нужно забывать, что производительность современной компьютерной системы определяется не только быстродействием отдельно взятого процессора, но и скоростями работы остальных узлов компьютера и даже способами организации всей системы в целом: очевидно, что чрезмерно быстрый процессор будет вынужден постоянно простаивать, ожидая, например, медленно работающую память; или другой пример – очень часто простое увеличение объема ОЗУ дает гораздо больший эффект, чем замена процессора на более быстрый.

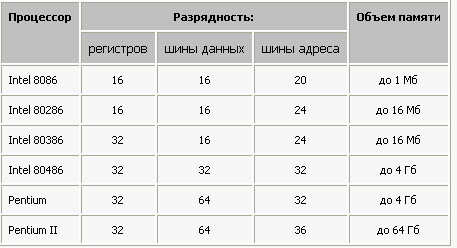

Косвенно скорость обработки информации зависит и еще от одного параметра процессора – его разрядности. Под разрядностью обычно понимают число одновременно обрабатываемых процессором битов. Формально эта величина есть количество двоичных разрядов в регистрах процессора и для современных моделей она равна 32. Тем не менее, все не так просто. Дело в том, что помимо описанной «внутренней» разрядности процессора существует еще разрядность шины данных, которой он управляет, и разрядность шины адреса [о шине более подробно рассказано в предыдущем билете]. Эти характеристики далеко не всегда совпадают (данные для таблицы взяты из книги М.Гука «Процессоры Intel: от 8086 до Pentium II». – СПб.: Питер, 1997):

Мы не будем обсуждать технические причины, по которым эти три разрядности могут различаться между собой, ибо причины эти сейчас представляют в основном исторический интерес. Отметим только, что разрядность регистров и разрядность шины данных влияют на длину обрабатываемых данных, а вот разрядность шины адреса R определяет максимальный объем памяти, который способен поддерживать процессор. Эту характеристику часто называют величиной адресного пространства, и она может быть вычислена по простой формуле 2R. Действительно, R двоичных разрядов позволяют получить именно такое количество неповторяющихся чисел, т.е. в данном случае адресов памяти.

Перейдем теперь к описанию основных характеристик памяти компьютера.

Хотя память компьютера состоит из отдельных битов, непосредственно «общаться» с каждым из них невозможно: биты группируются в более крупные блоки информации и именно они получают адреса, по которым происходит обращение к памяти. По сложившейся исторической традиции минимальная порция информации, которую современный компьютер способен записать в память составляет 8 бит или 1 байт. Отсюда становится очевидным, что общий объем памяти должен измеряться в байтах, или в производных от него единицах. Размер памяти персональных компьютеров стремительно возрастает. Первые модели имели 16-разрядное адресное пространство и, следовательно, объем памяти 216 = 64 Кбайта. Затем, когда памяти под разрабатываемые программные системы перестало хватать, инженеры введением некоторых весьма специфических способов формирования адреса увеличили ее размер на порядок – в MS DOS стандартная память была принята равной 640 Кбайт. Сейчас вы вряд ли сможете приобрести новый компьютер с ОЗУ менее 32-64 Мбайт, т.е. еще на два порядка больше (надеюсь, читатели не забыли, что 1 Мб = 1024 Кбайта).

Еще одной важной характеристикой памяти является время доступа или быстродействие памяти. Этот параметр определяется временем выполнения операций записи или считывания данных; он зависит от принципа действия и технологии изготовления запоминающих элементов.

Оставляя в стороне целый ряд других технологических характеристик современных запоминающих устройств, нельзя, тем не менее, пройти мимо статического и динамического устройства микросхем памяти. Статическая ячейка памяти – это специальная полупроводниковая схема (инженеры называют ее триггер), обладающая двумя устойчивыми состояниями. Одно из них принимается за логический ноль, а другое – за единицу. Состояния эти действительно настолько устойчивы, что при отсутствии внешних воздействий (и, конечно, подключенном напряжения питания!) могут сохраняться сколь угодно долго. Динамические ячейки памяти, напротив, не обладают этим свойством. Такие ячейки фактически представляют собой конденсатор, образованный элементами полупроводниковых микросхем. С некоторым упрощением можно сказать, что логической единице соответствует заряженный конденсатор, а нулю – незаряженный. Существенным свойством динамической ячейки памяти является наличие постепенного самопроизвольного разряда конденсатора через внешние схемы, что ведет к потере информации. Чтобы этого не происходило, конденсаторы динамической памяти необходимо периодически подзаряжать (такой процесс принято называть регенерацией ОЗУ). Оба вида запоминающих микросхем успешно конкурируют между собой, поскольку ни одна из них не является идеальной. С одной стороны, статическая память значительно проще в эксплуатации, т.к. не требует регенерации, и приближается по быстродействию к процессорным микросхемам. С другой стороны, она имеет меньший информационный объем и большую стоимость (в самом деле, изготовление конденсатора значительно проще, чем триггерной схемы и требует на кремниевой пластине гораздо меньше места), сильнее нагревается при работе. На практике в данный момент выбор микросхем для построения ОЗУ всегда решается в пользу динамической памяти. И все же быстродействующая статическая память в современном компьютере тоже обязательно есть: она называется кэш-памятью.

Этот вид памяти заслуживает отдельного рассмотрения. Он появился относительно недавно, но, начиная с 486 процессора, без кэш-памяти не обходится ни одна модель. Название кэш происходит от английского слова «cache», которое обозначает тайник или замаскированный склад (в частности, этим словом называют провиант, оставленный экспедицией для обратного пути или запас продуктов, например, зерна или меда, который животные создают на зиму). «Секретность» кэш заключается в том, что он невидим для пользователя и данные, хранящиеся там, недоступны для прикладного программного обеспечения. Процессор использует кэш исключительно самостоятельно, помещая туда извлеченные им из ОЗУ данные и команды программы и запоминая при этом в специальном каталоге адреса, откуда информация была извлечена. Если эти данные потребуются повторно, то уже не надо будет терять время на обращение к ОЗУ – их можно получить из кэш-памяти значительно быстрее. Поскольку объем кэш существенно меньше объема оперативной памяти, его контроллер (управляющая схема) тщательно следит за тем, какие данные следует сохранять в кэш, а какие заменять: удаляется та информация, которая используется реже или совсем не используется. Следует заметить, что кэш-память является очень эффективным средством повышения производительности компьютера, в чем легко убедиться на практике, если в вашем компьютере предусмотрена возможность отключения кэш.

В современных компьютерах кэш обычно строится по двухуровневой схеме. При этом первичный кэш встроен непосредственно внутрь процессора, а вторичный обычно устанавливается на системной плате. Как и для ОЗУ, увеличение объема кэш повышает эффективность работы компьютерной системы.

Литература

Информатика в понятиях и терминах: Кн. для учащихся ст. классов сред. шк./ Г.А. Бордовский, В.А. Извозчиков, Ю.В. Исаев, В.В. Морозов; Под ред. В.А. Извозчикова. - М.: Просвещение, 1991. - 208 с.

Радченко Н.П., Козлов О.А. Школьная информатика: экзаменационные вопросы и ответы. - М.: Финансы и статистика, 1998. - 160 с.

Семакин И., Залогова Л., Русаков С., Шестакова Л. Информатика. Учебник по базовому курсу (7-9 классы). М.: Лаборатория Базовых Знаний, 1998. - 464 с.

Кушниренко А.Г. и др. Основы информатики и вычислительной техники: Проб. учеб. для сред. учеб. заведений/ А.Г.Кушниренко, Г.В.Лебедев, Р.А.Сворень. - М.: Просвещение, 1990. - 224 с.

Гук М. Аппаратные средства IBM PC. Энциклопедия. СПб.: Издательство «Питер», 2000. - 816 c.

Операционная часть МП

Устройство управления …

Арифметико-логическое устройство …

Микропроцессорная память …

Процессор состоит из двух частей: -Шинного интерфейса -Операционного устройства Шинный интерфейс выбирает данные и команды из памяти. Он же записывает результаты в оперативную память. Операционная часть процессора состоит из двух частей: арифметико-логического устройства (АЛУ) и устройства управления (УУ). АЛУ выполняет арифметические и логические операции. УУ управляет порядком выборки команд и данных и записи результатов. В процессоре находятся регистры. Регистр - небольшая (32 бита), но очень быстродействующая область памяти. К регистрам, в отличии от ячеек оперативной памяти, обращаются не по адресам, а по именам. Все вычисления и выборка команд производятся только с помощью регистров, причем за некоторыми командами закреплены определенные регистры. Особенности архитектуры процессоров i 80486 и семейства Pentium Суперскалярная архитектура Конвейер - специальное устройство, которое разбивает выполнение команды на несколько этапов: Выборка команд из памяти и оперативной памяти. Декодирование команды (разбиение на микрокоманды). Генерация адреса, при которой определяются адреса операндов в памяти. Выполнение команды с помощью АЛУ Запись результата. Конвейер позволяет ускорить работу процессора, так как команда переходит из устройства выборки в устройство декодирования, и в устройство выборки можно поместить новую команду. В результате одновременно на конвейере может находиться 5 команд. Процессоры, имеющие 1 конвейер (i 80486), называются скалярными, а 2 и более (Pentium - 2 конвейера, семейство P6 (Pentium Pro/II/III) - 3 конвейера) - суперскалярными. Особенности архитектуры процессоров семейства P6 Раздельное кэширование кода и данных Кэширование - способ увеличения быстродействия системы, за счет хранения данных и команд в кэше (очень быстрой памяти), находящемся внутри процессора. Pentium содержит 2 блока кэш-памяти первого уровня (L 1) по 8 Кб: один для данных, другой для команд. Данные в кэш первого (L 1) поступают из кэша второго уровня (L 2) по 64-битной шине. Предсказание правильного адреса перехода Переход - запланированное изменение последовательного выполнения программы, обычно в каждых 6-8 командах содержится 1 команда перехода. Поэтому через каждые 6-8 команд приходится очищать конвейер и заполнять его заново. Поэтому в архитектуру Pentium'а был введен блок предсказания перехода. Имеется буфер меток перехода, который хранит информацию о последних 256 переходах. Блок предсказания перехода предполагает, что пройденная ветвь будет пройдена снова, соответствующая команда загружается на конвейер. Правильность предсказаний составляет 80%. Динамический анализ потока данных Проводится анализ зависимости команд от данных и регистров, для того чтобы оптимизировать поток команд. Главное - максимальная загрузка конвейера, ради этого нарушается порядок выполнения команд. Однако сбоев в выполнении программы не происходит, так как логика исполнения программы будет сохранена. Интеллектуальное исполнение Обозначает способность процессора выполнять неупорядоченные команды, а затем восстанавливать исходный порядок команд. Все промежуточные команды хранятся во временных регистрах, блок удаления и восстановления постоянно просматривает буфер команд, ищет те, которые уже выполнены и не имеют связи с другими командами. Такие команды удаляются, а сформированные ими данные помещаются в оперативную память или регистры, в том порядке, который предусмотрен программой. Порядок работы конвейера в процессорах семейства P6 Устройство шинного интерфейса посылает запросы оперативной памяти по системной шине. Считываемые данные помещаются в кэш второго уровня (L 2). Из кэша второго уровня (L 2) данные поступают в кэш данных первого уровня (L 1), а команды в кэш команд первого уровня (L 1). Запросы шинному интерфейсу на операнды команд посылаются устройством связи с памятью и буфером переупорядочивания запросов памяти. Устройство связи с памятью определяет какие операнды необходимы, а буфер переупорядочивания запросов памяти ищет их сначала в кэше данных первого уровня (L 1), затем в кэше второго уровня (L 2), а затем заставляет шинный интерфейс формировать запрос к оперативной памяти. Устройство выборки команд извлекает из кэша команд первого уровня (L 1) 32-байтную строку. Если среди выбранных команд встретилась команда перехода, то посылается запрос блоку вычисления адреса следующей команды. В этом блоке из команды считывается адрес перехода, и такой адрес ищется в буфере меток перехода. В буфере меток перехода хранится информация о последних 256 переходах. Если метка не найдена, тогда загружающиеся из памяти команды последовательно идут по конвейеру, пока команда перехода не дойдет до исполнительного устройства. Исполнительное устройство выполняет эту команду и определяет правильно ли была выполнена команда. Если да, то команда продолжает выполняться; если нет, то адрес перехода записывается в буфер меток перехода, конвейер очищается и загружается команда соответствующая адресу перехода. Если метка найдена в буфере меток перехода, предполагается, что пройденная ветвь будет пройдена снова, и загружается команда по адресу перехода. После выполнения команды перехода исполнительным устройством правильность перехода подтверждается или нет. Из устройства выборки команд команда попадает в устройство декодирования. В устройстве декодирования находится 3 декодера. Простые команды преобразуются в одну микрокоманду, а сложные в 2-4. Информация о преобразовании команд в микрокоманды хранится в устройстве командного управления. После декодирования микрокоманды могут выполняться в произвольном порядке и могут обращаться к одним и тем же регистрам. Во избежание конфликта используется набор из 40 временных регистров. Микрокоманды поступают в таблицу регистровых алиасов, где микрокомандам присваивается информация о соответствующих временных регистрах. Микрокоманды помещаются в буфер переупорядоченных команд. Буфер микрокоманд готовых к исполнению. Буфер микрокоманд готовых к исполнению просматривает буфер переупорядоченных команд и ищет готовые микрокоманды и посылает их в исполнительное устройство. Результаты выполнения команд снова помещаются в блок переупорядоченных команд. Команды выполняются с помощью пяти исполнительных устройств. Целочисленное устройство кроме вычислений определяет правильность перехода. Блок удаления и восстановления просматривает блок переупорядоченных команд, находит выполненные команды и удаляет их. Удаленные микрокоманды восстанавливаются в исходном порядке и результаты вычисления записываются в регистры и оперативную память.

Интерфейсная часть МП

Интерфейсная часть МП предназначена для связи и согласования МП системной шиной ПК, а также для приема, предварительного анализа команд выполняемой программы и формирования полных адресов операндов и команд. Интерфейсная часть включает в свой состав адресные регистры МПП, узел формирования адреса, блок регистров команд, являющийся буфером команд в МП, внутреннюю интерфейсную шину МП и схемы управления шиной и портами ввода-вывода.

Список источников из Интернет